Alberto Bosio Daniel Ménard Olivier Sentieys *Editors*

# Approximate Computing Techniques

From Component- to Application-Level

Approximate Computing Techniques

Alberto Bosio • Daniel Ménard • Olivier Sentieys Editors

# Approximate Computing Techniques

From Component- to Application-Level

*Editors* Alberto Bosio University of Lyon, ECL, INSA Lyon, CNRS, UCBL, CPE Lyon, INL, UMR5270 Écully, France

Olivier Sentieys University of Rennes, INRIA/IRISA Lannion, France Daniel Ménard Univ. Rennes, INSA Rennes, IETR, Rennes, France

# ISBN 978-3-030-94704-0 ISBN 978-3-030-94705-7 (eBook) https://doi.org/10.1007/978-3-030-94705-7

### © Springer Nature Switzerland AG 2022

This work is subject to copyright. All rights are reserved by the Publisher, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, reuse of illustrations, recitation, broadcasting, reproduction on microfilms or in any other physical way, and transmission or information storage and retrieval, electronic adaptation, computer software, or by similar or dissimilar methodology now known or hereafter developed.

The use of general descriptive names, registered names, trademarks, service marks, etc. in this publication does not imply, even in the absence of a specific statement, that such names are exempt from the relevant protective laws and regulations and therefore free for general use.

The publisher, the authors and the editors are safe to assume that the advice and information in this book are believed to be true and accurate at the date of publication. Neither the publisher nor the authors or the editors give a warranty, expressed or implied, with respect to the material contained herein or for any errors or omissions that may have been made. The publisher remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

This Springer imprint is published by the registered company Springer Nature Switzerland AG The registered company address is: Gewerbestrasse 11, 6330 Cham, Switzerland

# Contents

| 1   | General Introduction<br>Alberto Bosio, Daniel Ménard, and Olivier Sentieys                                                       | 1   |

|-----|----------------------------------------------------------------------------------------------------------------------------------|-----|

| Par | rt I Techniques for Approximate Computing                                                                                        |     |

| 2   | Customizing Number Representation and Precision<br>Olivier Sentieys and Daniel Ménard                                            | 11  |

| 3   | Hardware Level Approximations<br>Ioannis Tsiokanos, George Papadimitriou, Dimitris Gizopoulos,<br>and Georgios Karakonstantis    | 43  |

| 4   | Inexact Arithmetic Operators<br>Lukas Sekanina, Zdenek Vasicek, and Vojtech Mrazek                                               | 81  |

| 5   | Approximate Computing at the Algorithmic Level<br>Justine Bonnot, Alexandre Mercat, Erwan Nogues,<br>and Daniel Ménard           | 109 |

| Par | rt II Methods and Tools for Approximate Computing                                                                                |     |

| 6   | Analysis of the Impact of Approximate Computing on the<br>Application Quality<br>Justine Bonnot, Daniel Ménard, and Karol Desnos | 145 |

| 7   | Accuracy-Aware Compilers<br>Sasa Misailovic                                                                                      | 177 |

| 8   | <b>Design Space Exploration Tools</b><br>Mario Barbareschi, Salvatore Barone, Nicola Mazzocca,<br>and Alberto Moriconi           | 215 |

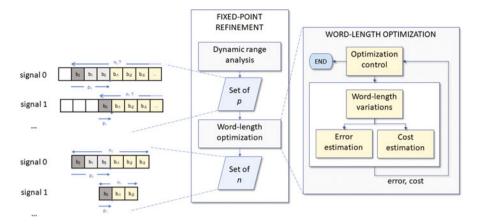

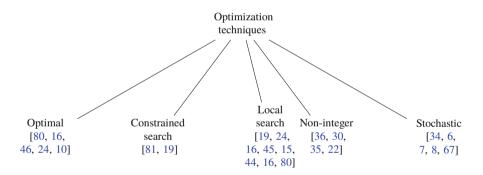

| 9   | Wordlength Optimization of Fixed-Point Algorithms<br>Gabriel Caffarena                                                           | 261 |

| Par | t III Approximate Computing Applied to Real-Life<br>Applications                                                                                                                                                                                                                          |     |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

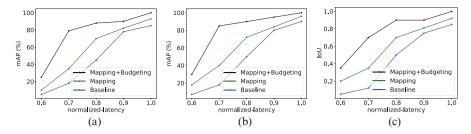

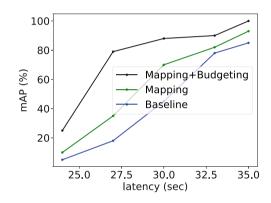

| 10  | <b>Exploiting Approximations in Real-Time Scheduling</b><br>Kamyar Mirzazad Barijough, Lin Huang, I-Hong Hou,<br>Sachin S. Sapatnekar, Jiang Hu, and Andreas Gerstlauer                                                                                                                   | 287 |

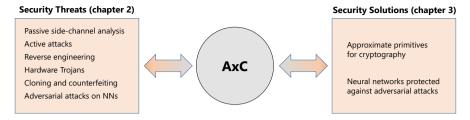

| 11  | Security in an Approximated World: New Threats and<br>Opportunities in the Approximate Computing Paradigm<br>Paolo Palmieri, Ilia Polian, and Francesco Regazzoni                                                                                                                         | 323 |

| 12  | Design, Verification, Test, and In-Field Implications of<br>Approximate Digital Integrated Circuits<br>Alberto Bosio, Stefano Di Carlo, Patrick Girard, Annachiara Ruospo,<br>Ernesto Sanchez, Alessandro Savino, Lukas Sekanina,<br>Marcello Traiola, Zdenek Vasicek, and Arnaud Virazel | 349 |

| 13  | Approximate Computing for Fault Tolerance Mechanisms<br>for Safety-Critical Applications                                                                                                                                                                                                  | 387 |

| 14  | Approximate Computing for Scientific Applications<br>Hartwig Anzt, Marc Casas, A. Cristiano I. Malossi,<br>Enrique S. Quintana-Ortí, Florian Scheidegger, and Sicong Zhuang                                                                                                               | 415 |

| 15  | Approximations in Deep Learning<br>Etienne Dupuis, Silviu Filip, Olivier Sentieys, David Novo,<br>Ian O'Connor, and Alberto Bosio                                                                                                                                                         | 467 |

| Ind | ex                                                                                                                                                                                                                                                                                        | 513 |

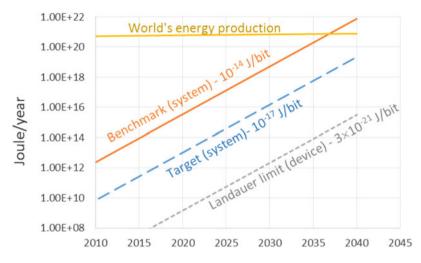

| Energy consumption trends in computing versus the              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|----------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| world energy production. Source: SIA/SRC [3]                   | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

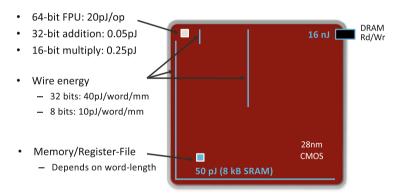

| Energy cost in a processor. Source: [4]                        | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

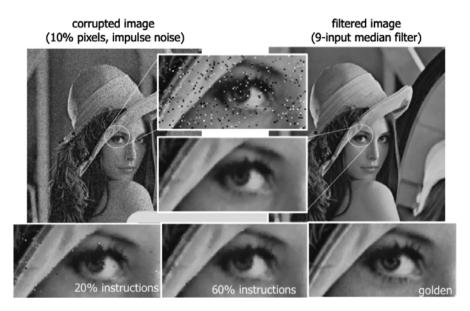

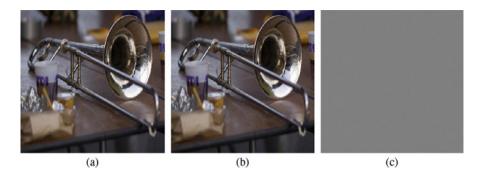

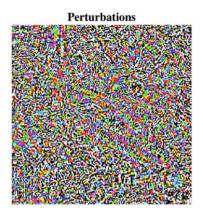

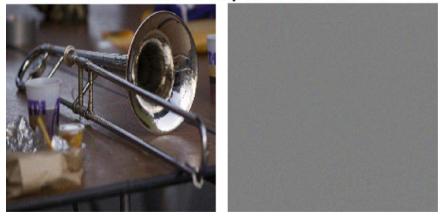

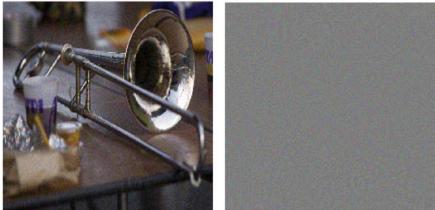

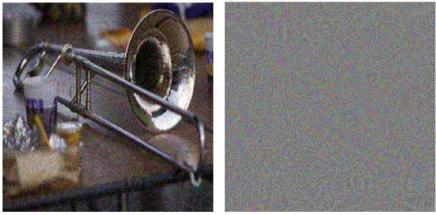

| Perceptual limitation and removal of instructions.             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Source: courtesy of Lukas Sekanina                             | 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

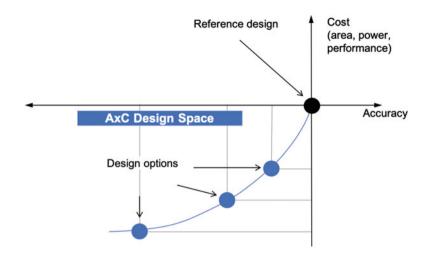

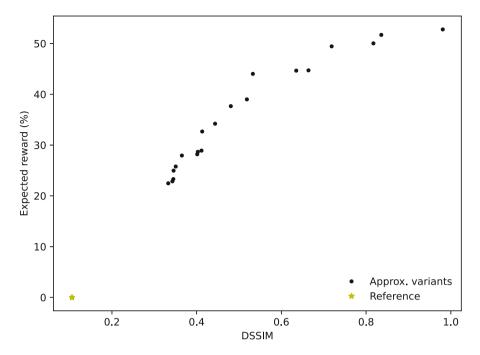

| AxC design space exploration: accuracy vs. cost                | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

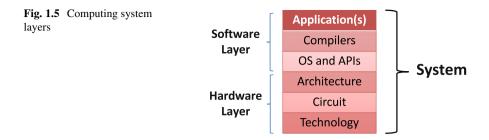

| Computing system layers                                        | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

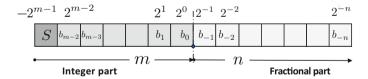

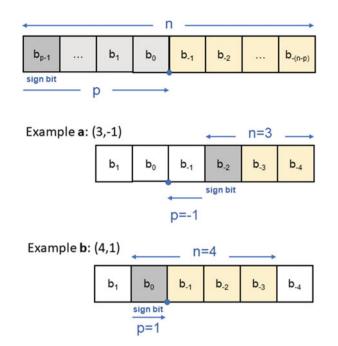

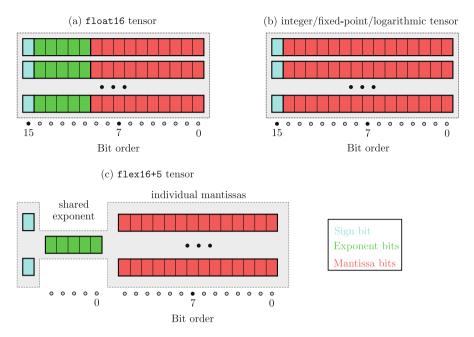

| Fixed-point specification                                      | 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

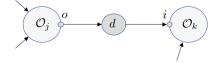

| Example of a sequence of operations: data $d$ is the           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| output of the operation $O_j$ and the input of operation $O_k$ | 19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

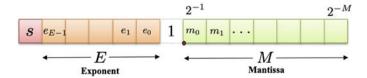

|                                                                | 21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

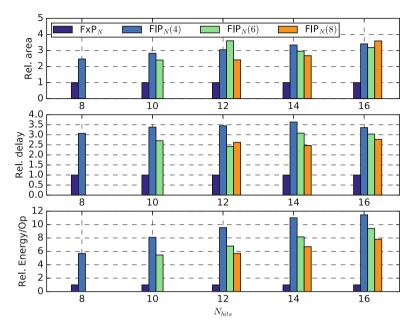

| Relative area, delay, and energy per operation between         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| fixed-point and floating-point of adders for different         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| bit-widths                                                     | 31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

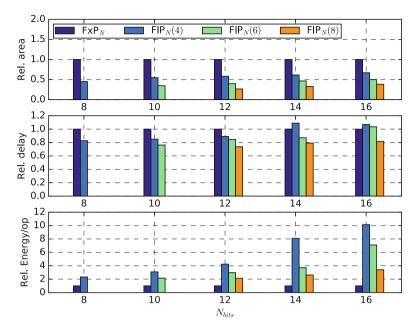

| Relative area, delay, and energy per operation between         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| fixed-point and floating-point of multipliers for different    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                                                | 32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

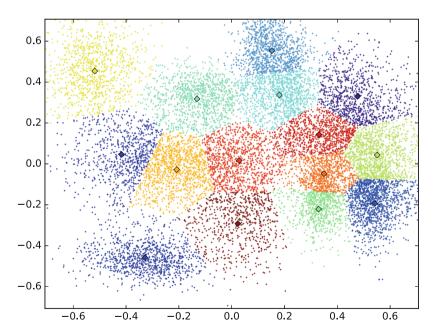

|                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                                                | 33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

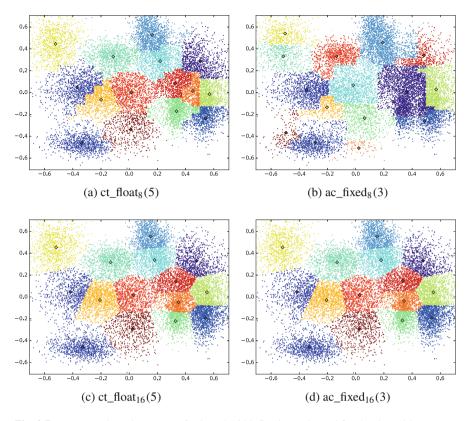

|                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                                                | 37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                                                | 38                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                                                | 39                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

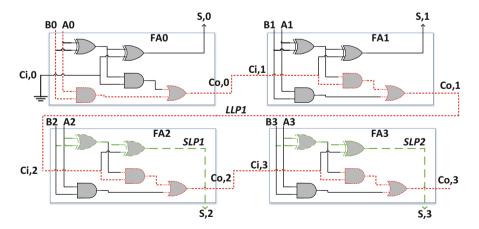

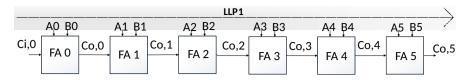

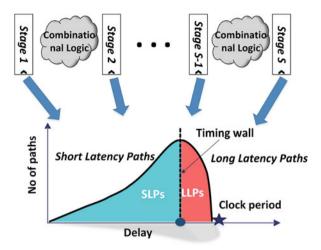

| (SLP1 and SLP2)                                                | 45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

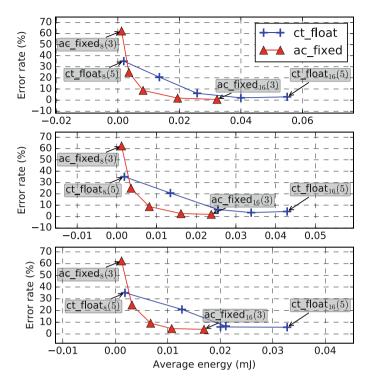

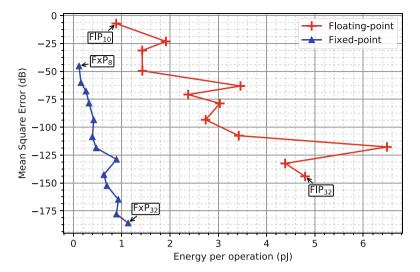

|                                                                | world energy production. Source: SIA/SRC [3]<br>Energy cost in a processor. Source: [4]<br>Perceptual limitation and removal of instructions.<br>Source: courtesy of Lukas Sekanina<br>AxC design space exploration: accuracy vs. cost<br>Computing system layers<br>Fixed-point specification<br>Example of a sequence of operations: data <i>d</i> is the<br>output of the operation $O_j$ and the input of operation $O_k$<br>Floating-point representation<br>Relative area, delay, and energy per operation between<br>fixed-point and floating-point of adders for different<br>bit-widths<br>Relative area, delay, and energy per operation between<br>fixed-point and floating-point of multipliers for different<br>bit-widths<br>2D K-means clustering golden output example, obtained<br>using double-precision (64-bit) floating-point<br>K-means clustering outputs for 8- and 16-bit<br>floating-point and fixed-point, with accuracy target of<br>$10^{-4}$ . (a) ct_float8(5). (b) ac_fixed8(3). (c) ct_float16(5).<br>(d) ac_fixed16(3)<br>Energy vs. classification error rate for K-Means<br>clustering with stopping conditions of $10^{-4}$ (top), $10^{-3}$<br>(centre) and $10^{-2}$ (bottom)<br>Fixed-point and floating-point energy per operation (pJ)<br>vs MSE for FFT-16 for different bit-widths<br>Data-paths in a 4-bit ripple carry adder, highlighting the<br>longest latency path ( <i>LLP1</i> ) and two short latency paths |

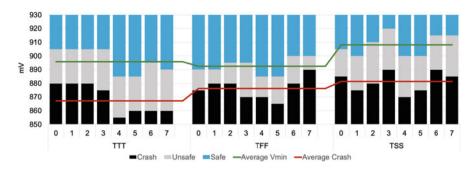

| Fig. 3.2              | X-Gene 2 characterization results for one benchmark on<br>three different chips (TTT, TFF, and TSS). Blue colour |    |

|-----------------------|------------------------------------------------------------------------------------------------------------------|----|

|                       | in bars represents the Safe region, grey represents the<br>Unsafe region, and black represents the Crash region  | 52 |

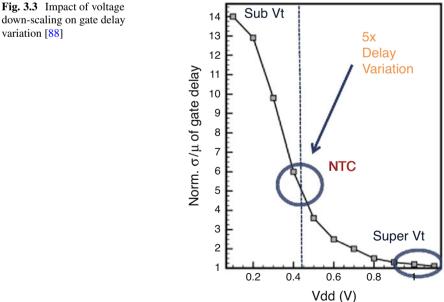

| Fig. 3.3              | Impact of voltage down-scaling on gate delay                                                                     |    |

| E'. 2.4               | variation [88]                                                                                                   | 54 |

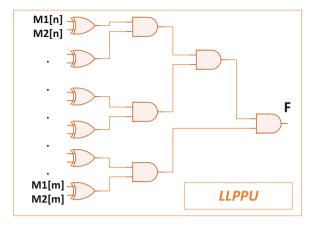

| Fig. 3.4<br>Fig. 3.5  | Carry propagation in a 6-bit ripple carry adder (RCA)<br>Block diagram of the long latency paths prediction unit | 58 |

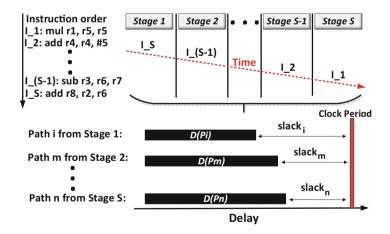

| Fig. 3.6              | (LLPPU)<br>Instruction flow and delay requirements across different                                              | 59 |

| <b>F</b> : 0 <b>7</b> | paths and stages in a pipelined core                                                                             | 60 |

| Fig. 3.7              | Conventional path distribution of a pipelined design                                                             | 61 |

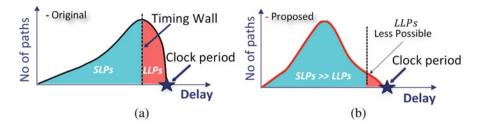

| Fig. 3.8              | (a) Conventional path distribution and (b) path distribution after applying path shaping                         | 62 |

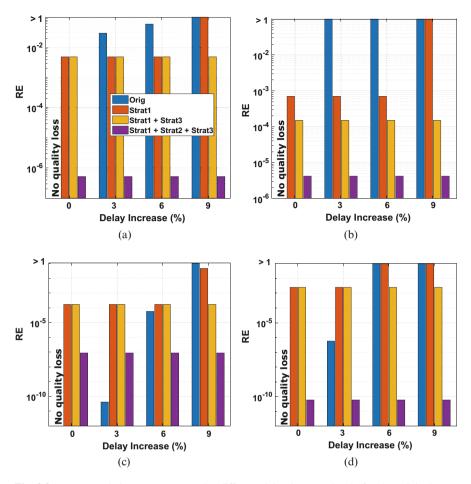

| Fig. 3.9              | Average relative error (RE) under different delay                                                                |    |

| 1.8.01                | increase levels for the original FPU with ( <i>Strat</i> 1)                                                      |    |

|                       | and without statically truncating the 44 LSBs (Orig),                                                            |    |

|                       | the FPU when path shaping and static truncation                                                                  |    |

|                       | of 44 LSB are enabled ( $Strat1 + Strat3$ ), and the                                                             |    |

|                       | FPU when path shaping, timing error prediction, and                                                              |    |

|                       | dynamic truncation of 44 LSBs are jointly considered                                                             |    |

|                       | (Strat1 + Strat2 + Strat3). (a) Raytrace. (b) CFD.                                                               |    |

|                       | (c) K-means. (d) Heartwall $\dots$                                                                               | 64 |

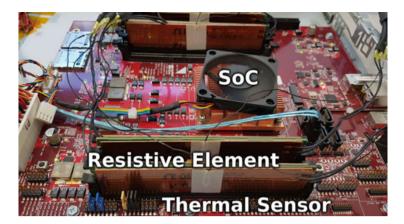

| Fig. 3.10             | X-Gene 2 with the custom thermal adapters                                                                        | 68 |

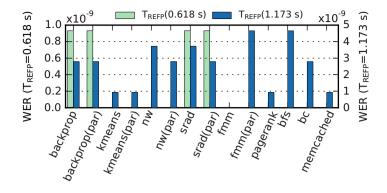

| Fig. 3.11             | WER for DRAM operating under 0.618 s and 1.173 s at                                                              | 08 |

| Fig. 5.11             | 50 °C                                                                                                            | 69 |

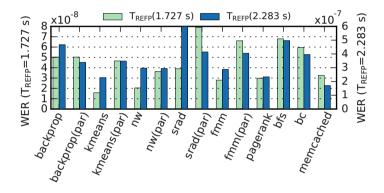

| Fig. 3.12             | WER for DRAM operating under 1.727 s and 2.283 s at                                                              | 09 |

| Fig. 5.12             | 50°C                                                                                                             | 69 |

| Fig. 3.13             | Temperature controller board [147]                                                                               | 70 |

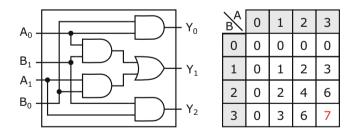

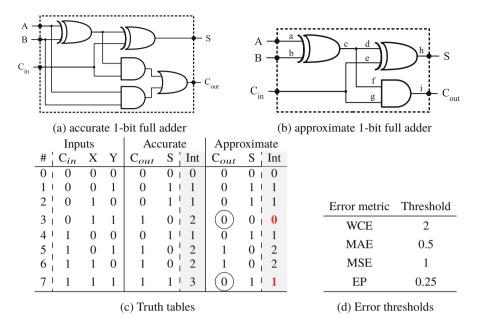

| Fig. 4.1              | The 2-bit approximate multiplier proposed by Kulkarni                                                            |    |

| U                     | et al. in [13] and its specification                                                                             | 84 |

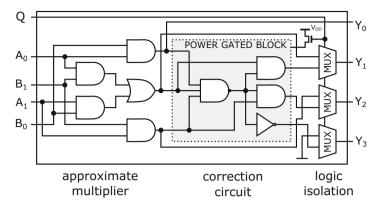

| Fig. 4.2              | Quality configurable 2-bit multiplier according to [17]                                                          | 86 |

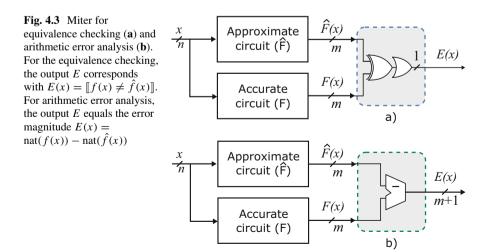

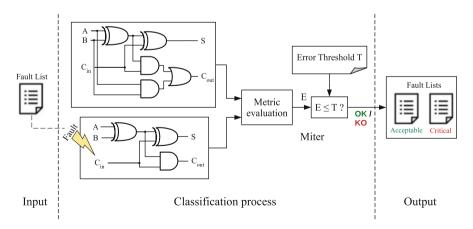

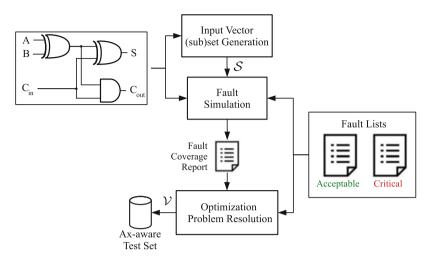

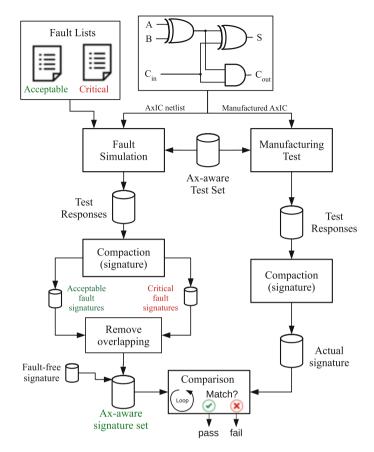

| Fig. 4.3              | Miter for equivalence checking (a) and arithmetic error                                                          |    |

| U U                   | analysis (b). For the equivalence checking, the output                                                           |    |

|                       | <i>E</i> corresponds with $E(x) = [f(x) \neq \hat{f}(x)]$ . For                                                  |    |

|                       | arithmetic error analysis, the output $E$ equals the error                                                       |    |

|                       | magnitude $E(x) = nat(\hat{f}(x)) - nat(\hat{f}(x))$                                                             | 89 |

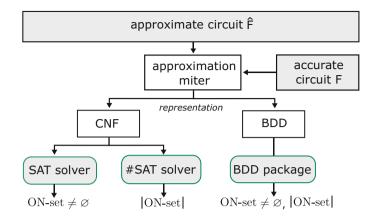

| Fig. 4.4              | Overview of formal error analysis approaches                                                                     | 90 |

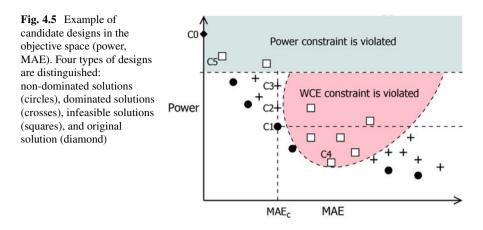

| Fig. 4.5              | Example of candidate designs in the objective space                                                              |    |

| 0                     | (power, MAE). Four types of designs are distinguished:                                                           |    |

|                       | non-dominated solutions (circles), dominated solutions                                                           |    |

|                       | (crosses), infeasible solutions (squares), and original                                                          |    |

|                       | solution (diamond)                                                                                               | 93 |

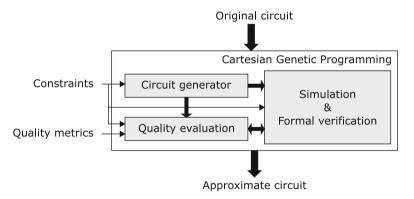

| Fig. 4.6              | Employing Cartesian genetic programming for                                                                      | 20 |

| -0                    | automated design of approximate circuits                                                                         | 98 |

|                       | U 11                                                                                                             | -  |

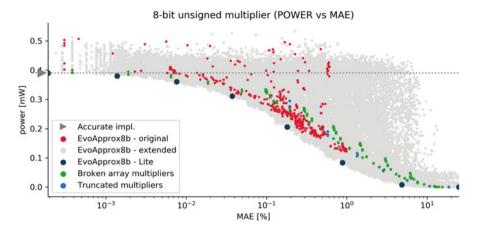

| Fig. 4.7              | The 8-bit approximate multipliers (black points) that<br>were selected to EvoApprox8b-Lite from all the evolved           |     |

|-----------------------|---------------------------------------------------------------------------------------------------------------------------|-----|

|                       | approximate multipliers (gray points) and compared to                                                                     |     |

|                       | the former version of EvoApprox8b library (red points),                                                                   |     |

|                       | broken array multipliers (green points) and truncated                                                                     |     |

|                       | multipliers (blue points)                                                                                                 | 100 |

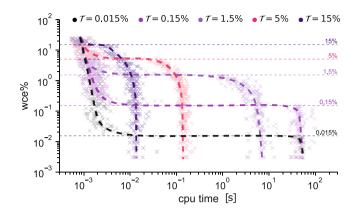

| Fig. 4.8              | The computational requirements of the WCEGT                                                                               | 100 |

| 115. 1.0              | procedure proving that $e_{wce} > \mathcal{T}$ of 8-bit approximate                                                       |     |

|                       | multipliers taken from EvoApprox library $\dots$                                                                          | 101 |

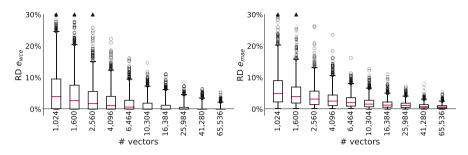

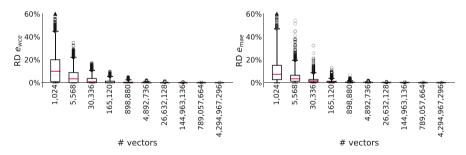

| Fig. 4.9              | Relative difference between exact and estimated errors                                                                    | 101 |

| 1 lg. 4.)             | for 8-bit approximate multipliers. The whiskers show                                                                      |     |

|                       | the 2nd percentile and the 98th percentile. Triangles                                                                     |     |

|                       | indicate that there is even higher RD than shown                                                                          | 102 |

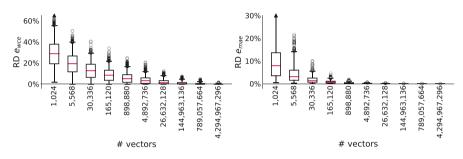

| Fig. 4.10             | Relative difference between exact and estimated errors                                                                    | 102 |

| 11g. 4.10             | for 16-bit approximate multipliers. The whiskers show                                                                     |     |

|                       |                                                                                                                           |     |

|                       | the 2nd percentile and the 98th percentile. Triangles indicate that there is even higher RD than shown                    | 102 |

| Eig 4 11              | · · · · · · · · · · · · · · · · · · ·                                                                                     | 102 |

| Fig. 4.11             | Relative difference between exact and estimated errors<br>for 16-bit approximate adders. The whiskers show the            |     |

|                       | 2nd percentile and the 98th percentile. Triangles indicate                                                                |     |

|                       |                                                                                                                           | 102 |

| Eig 51                | that there is even higher RD than shown                                                                                   | 102 |

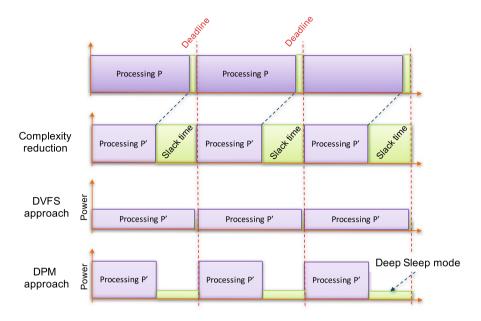

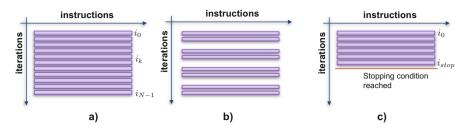

| Fig. 5.1              | Exploitation of slack time to reduce the energy                                                                           |     |

|                       | consumption for real-time processing. (a) Initial                                                                         | 110 |

| E. 5.0                | processing. (b) DPM approach. (c) DVFS approach                                                                           | 110 |

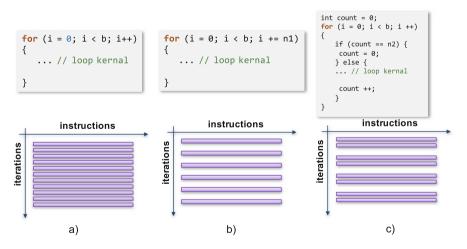

| Fig. 5.2              | Illustration of the loop perforation concept. (a) Initial                                                                 |     |

|                       | <i>for-loop</i> . (b) Loop perforation with the execution of one iteration loop of term (c) Loop performing with the ship |     |

|                       | iteration loop after $n_1$ . (c) Loop perforation with the skip                                                           | 110 |

| E:- 5.2               | of one iteration after $n_2$                                                                                              | 112 |

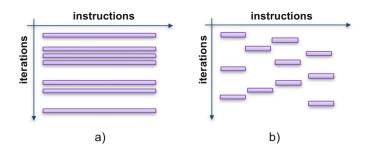

| Fig. 5.3              | Illustration of the loop perforation concept at run-time.                                                                 |     |

|                       | (a) Dynamic perforation: the number of skipped                                                                            | 114 |

| E. 5.4                | iterations is decided at run-time. (b) Selective perforation                                                              | 114 |

| Fig. 5.4              | Illustration of the difference between loop perforation                                                                   |     |

|                       | and early termination for an iterative refinement                                                                         |     |

|                       | algorithm. (a) Initial iterative refinement algorithm. (b)                                                                |     |

|                       | Loop perforation. (c) Early termination. The process is                                                                   | 115 |

| <b>F</b> : <i>E E</i> | stopped when the condition criterion is reached                                                                           | 115 |

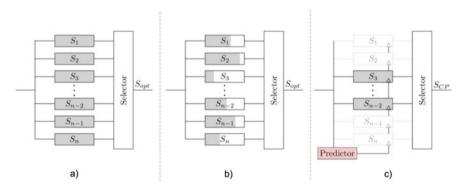

| Fig. 5.5              | Three techniques to handle OSSE algorithms. (a)                                                                           |     |

|                       | Exhaustive search: each branch represents a full solution                                                                 |     |

|                       | computation. (b) Early termination: the exploration                                                                       |     |

|                       | of branches which cannot lead to the best solution is                                                                     |     |

|                       | stopped before the end. (c) SSSR technique: coarse                                                                        |     |

|                       | estimation is carried-out and a refinement is applied to                                                                  | 117 |

| <b>D</b> ' <b>C C</b> | the best candidates                                                                                                       | 116 |

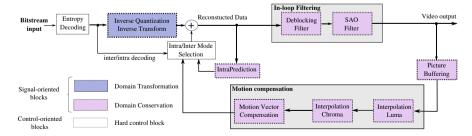

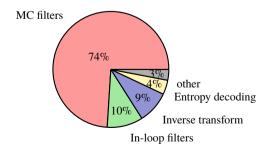

| Fig. 5.6              | Algorithm classification of an HEVC decoder                                                                               | 125 |

| Fig. 5.7  | Average relative complexity of data processing blocks<br>in an optimized HEVC decoder on a general purpose |     |

|-----------|------------------------------------------------------------------------------------------------------------|-----|

|           | processor. Input sequences: Kimono RA 1920x1080                                                            |     |

|           | with Quantization Parameter from 22 to 32 by steps of 2                                                    | 126 |

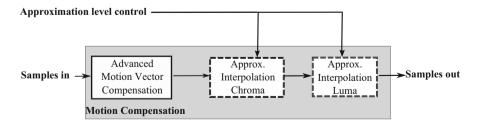

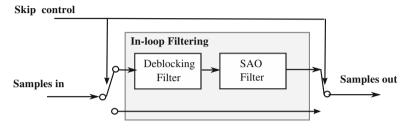

| Fig. 5.8  | Interpolation filter of the MC block approximation                                                         | 120 |

| Fig. 5.9  | In-loop filter skip                                                                                        | 127 |

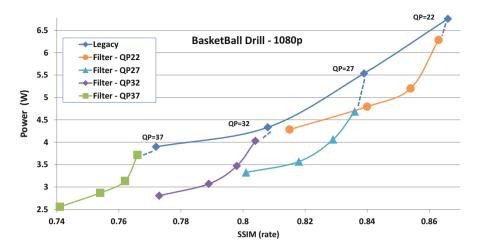

| Fig. 5.10 | Power consumption of <i>computation approximation</i>                                                      | 120 |

| 11g. 5.10 | decoder vs SSIM distortion                                                                                 | 130 |

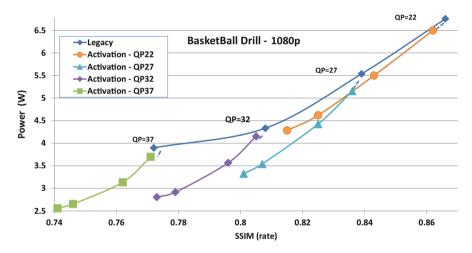

| Fig. 5.11 | Power consumption of <i>computation skip</i> decoder vs                                                    | 150 |

| 115. 5.11 | SSIM distortion                                                                                            | 130 |

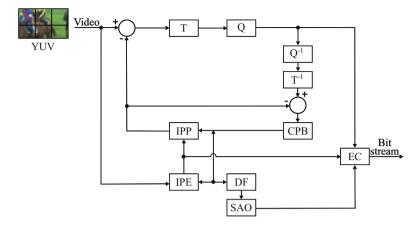

| Fig. 5.12 | Block diagram of HEVC intra encoder composed by                                                            | 100 |

|           | several blocks: Intra Picture Process (IPP), Intra Picture                                                 |     |

|           | Estimation (IPE), Transform (T), Quantization (Q),                                                         |     |

|           | Inverse Quantization $(Q^{-1})$ , Inverse Transform $(T_{-1})$ ,                                           |     |

|           | Current Picture Buffer (CPB), Deblocking Filter (DF),                                                      |     |

|           | Sample-Adaptive Offset (SAO) and Entropy Coding                                                            |     |

|           | (EC)                                                                                                       | 131 |

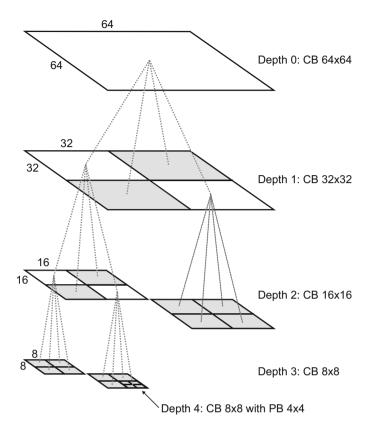

| Fig. 5.13 | Quad-tree structure of a Coding Tree Block (CTB)                                                           |     |

| 0         | divided into Coding Block (CB)                                                                             | 132 |

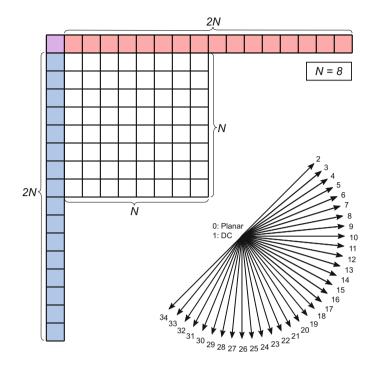

| Fig. 5.14 | Neighboring samples used for intra-prediction in an                                                        |     |

| 0         | $N \times N$ PB with $N = 8$ and intra-prediction modes                                                    | 133 |

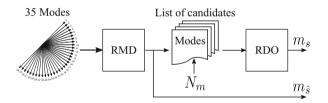

| Fig. 5.15 | Intra-prediction steps                                                                                     | 133 |

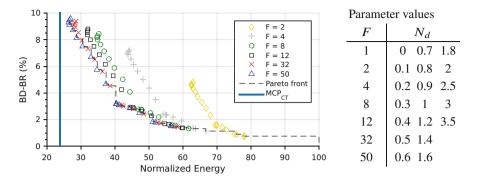

| Fig. 5.16 | Pareto in Rate-Energy space from the set of parameters                                                     |     |

|           | $F$ and $N_d$                                                                                              | 136 |

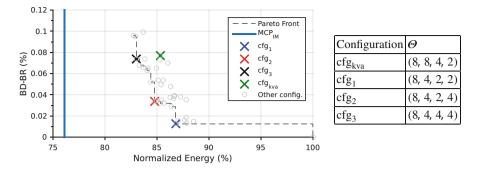

| Fig. 5.17 | Pareto in Rate-Energy space generated from all                                                             |     |

| -         | $3 \times 3 \times 2 \times 2 = 36$ combinations of parameter values                                       | 137 |

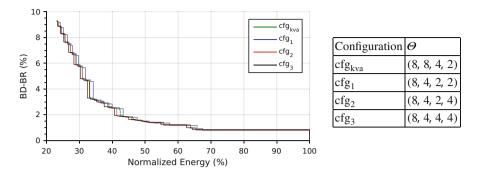

| Fig. 5.18 | Pareto in Rate-Energy space from the set of $\Theta$ defined                                               |     |

|           | in the table                                                                                               | 138 |

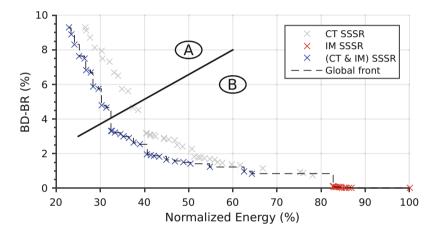

| Fig. 5.19 | Pareto in Rate-Energy space from the CT OSSE, the IM                                                       |     |

|           | OSSE and the combination of the two OSSE: CT & IM                                                          | 138 |

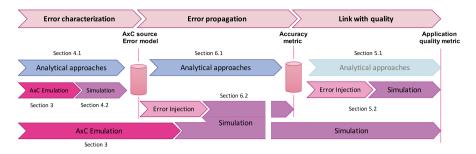

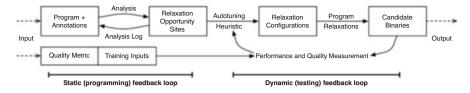

| Fig. 6.1  | Different steps to analyze the impact of approximation                                                     |     |

|           | on quality                                                                                                 | 146 |

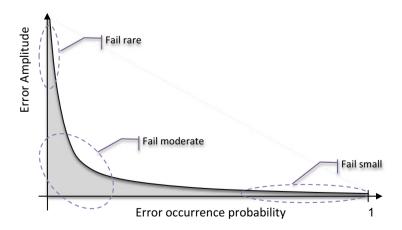

| Fig. 6.2  | Evolution of maximal error amplitude according to its                                                      |     |

|           | occurrence probability                                                                                     | 147 |

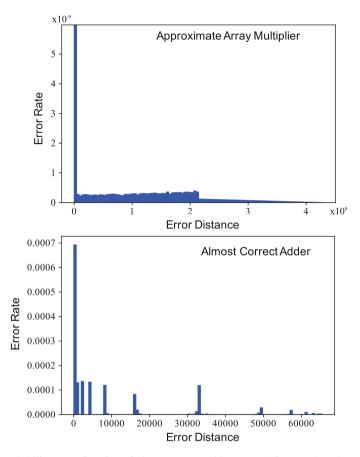

| Fig. 6.3  | Probability mass function of almost correct adder,                                                         |     |

|           | N = 16, C = 4, and approximate array multiplier,                                                           |     |

|           | N = 16                                                                                                     | 150 |

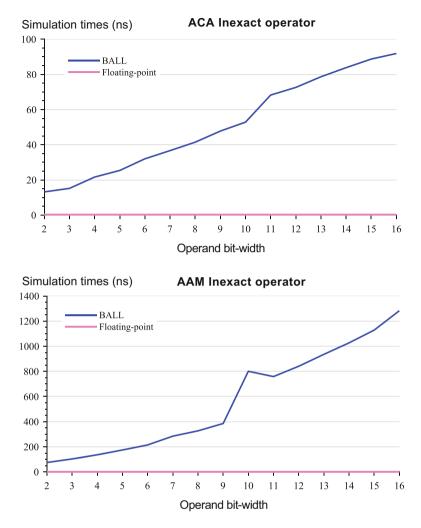

| Fig. 6.4  | Comparison of the simulation time for the BALL and                                                         |     |

|           | floating-point simulation of two inexact arithmetic operators                                              | 153 |

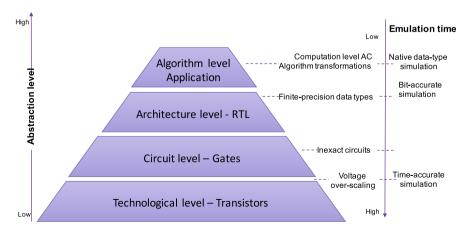

| Fig. 6.5  | The different abstraction levels and times for emulation                                                   | 155 |

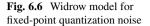

| Fig. 6.6  | Widrow model for fixed-point quantization noise                                                            | 157 |

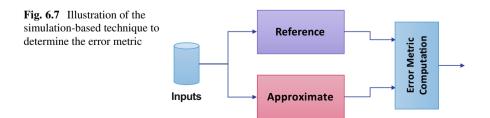

| Fig. 6.7  | Illustration of the simulation-based technique to                                                          |     |

|           | determine the error metric                                                                                 | 161 |

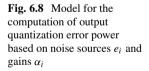

| Fig. 6.8  | Model for the computation of output quantization error                                                     |     |

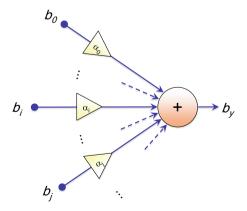

|           | power based on noise sources $e_i$ and gains $\alpha_i$                                                    | 168 |

|           |                                                                                                            |     |

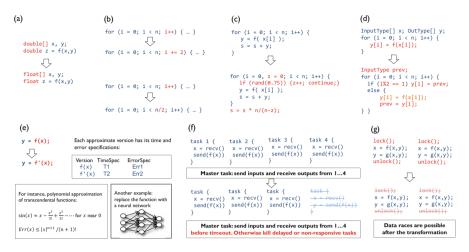

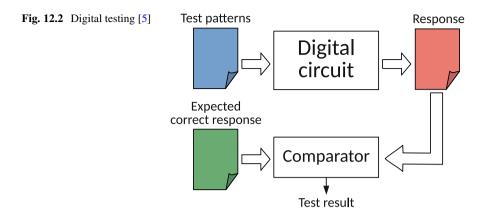

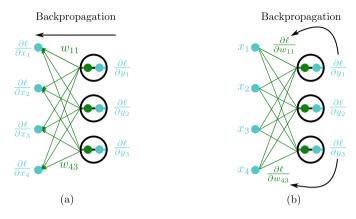

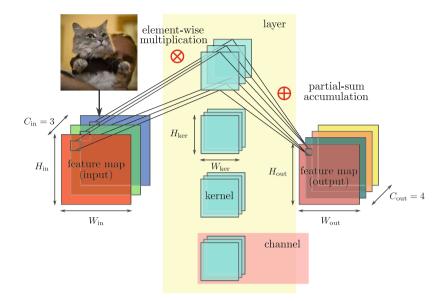

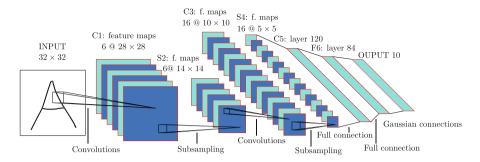

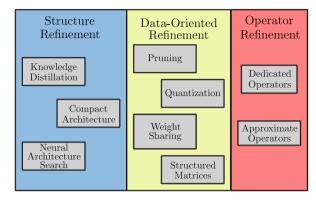

| Fig. 7.1                        | Examples of accuracy-aware optimizations (the approximation code is marked in red). (a) Data structure |            |

|---------------------------------|--------------------------------------------------------------------------------------------------------|------------|

|                                 | optimization. (b) Loop perforation. (c) Reduction                                                      |            |

|                                 | sampling. (d) Approximate tiling. (e) Function                                                         |            |

|                                 | substitution. (f) Dropping tasks. (g) Remove locks                                                     | 181        |

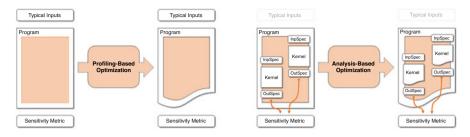

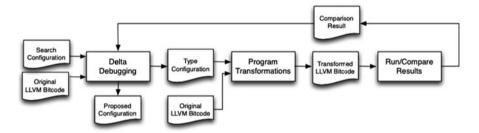

| Fig. 7.2                        | The approaches for accuracy-aware optimization.                                                        |            |

|                                 | We start with the original program and produce the                                                     |            |

|                                 | approximate program. The analysis-based compiler                                                       |            |

|                                 | takes into consideration the annotations on the kernels,                                               |            |

|                                 | while the profiling-based compiler treats the whole                                                    |            |

|                                 | program as one entity                                                                                  | 183        |

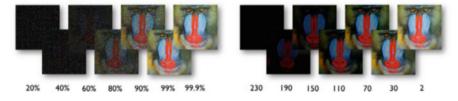

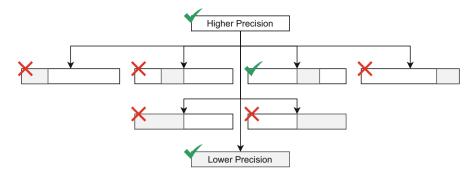

| Fig. 7.3                        | The impact of errors on end-to-end acceptability: the                                                  |            |

|                                 | kernel computation calculates the correct pixel value                                                  |            |

|                                 | with only specified frequency (left) or computes it with                                               |            |

|                                 | the specified absolute error in each pixel component                                                   |            |

|                                 | (right)                                                                                                | 184        |

| Fig. 7.4                        | Sensitivity profiling finds the set of perforatable loops S                                            |            |

|                                 | in application A given representative inputs I, accuracy                                               |            |

|                                 | metric $Q$ , and accuracy goal $b$                                                                     | 188        |

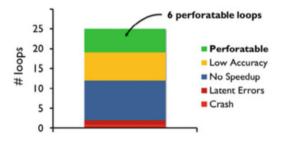

| Fig. 7.5                        | Results of sensitivity profiling of x264                                                               | 191        |

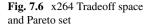

| Fig. 7.6                        | x264 Tradeoff space and Pareto set                                                                     | 192        |

| Fig. 7.7                        | Chisel overview                                                                                        | 194        |

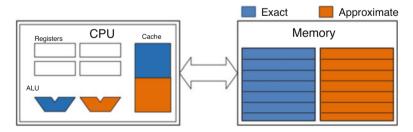

| Fig. 7.8                        | Model of approximate hardware, with exact (blue) and                                                   |            |

|                                 | approximate (orange) components                                                                        | 195        |

| Fig. 7.9                        | Chisel's intermediate language                                                                         | 197        |

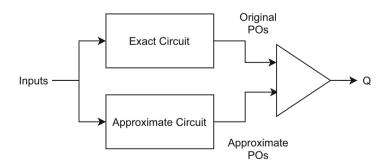

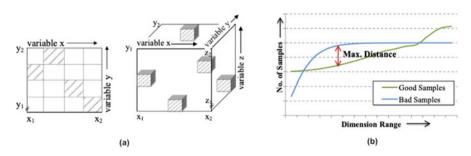

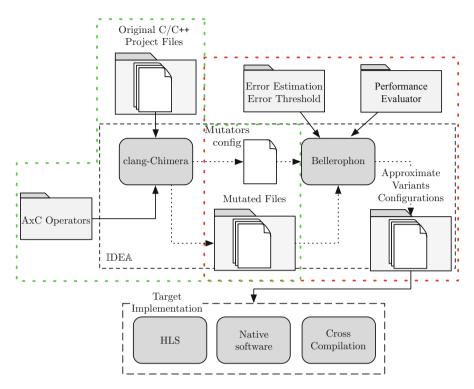

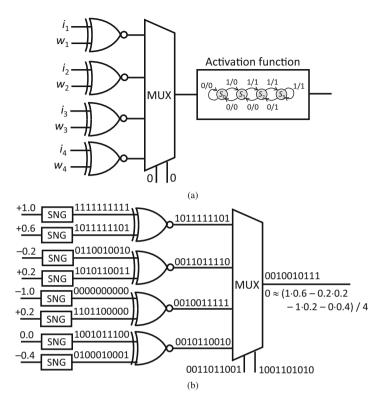

| Fig. 8.1                        | Quality constraint circuit [25]                                                                        | 220        |

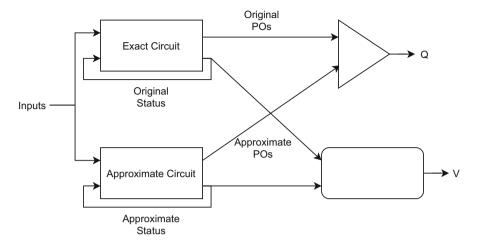

| Fig. 8.2                        | Sequential quality constraint circuit [27]                                                             | 223        |

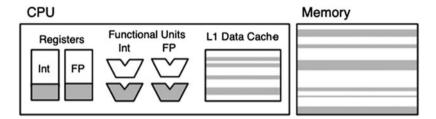

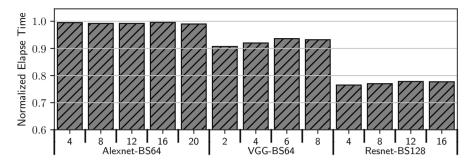

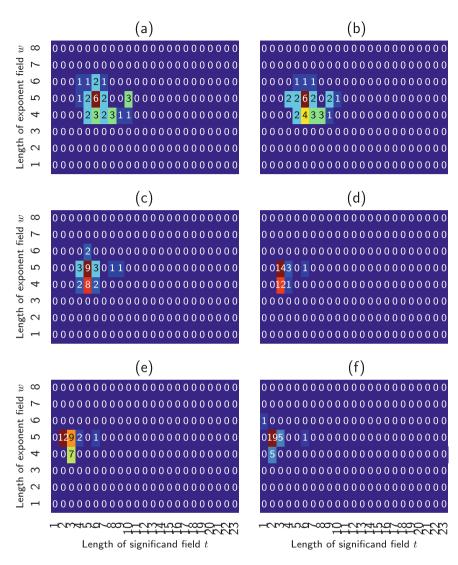

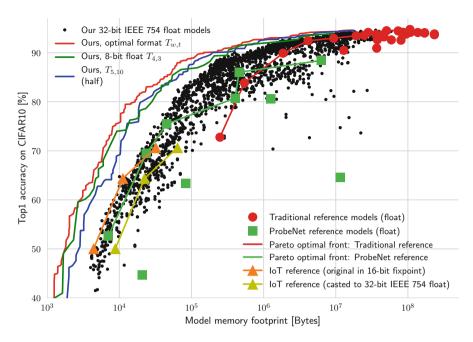

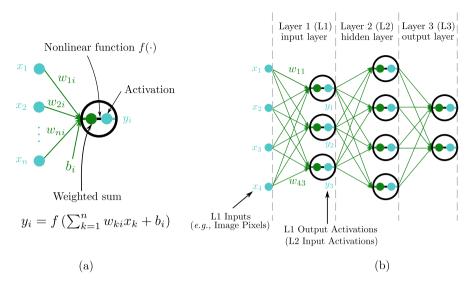

| Fig. 8.3                        | Hardware model used for simulation in [44]                                                             | 232        |